# CSE 2600 Intro. To Digital Logic & Computer Design

Bill Siever & Michael Hall

#### This week

- Homework 8 Optional, extra credit

- Hard deadline of submission to Gradescope on Wed, Dec. 3 by 11:59 pm.

- Must demo to either Prof. Hall or Siever by the 12<sup>th</sup>

- Additional office hours will be posted for the 8-12<sup>th</sup>

#### **Studio Review**

- Control Signals...

- jal encoding / impact

- riscvsingle.sv

# **Chapter 7**

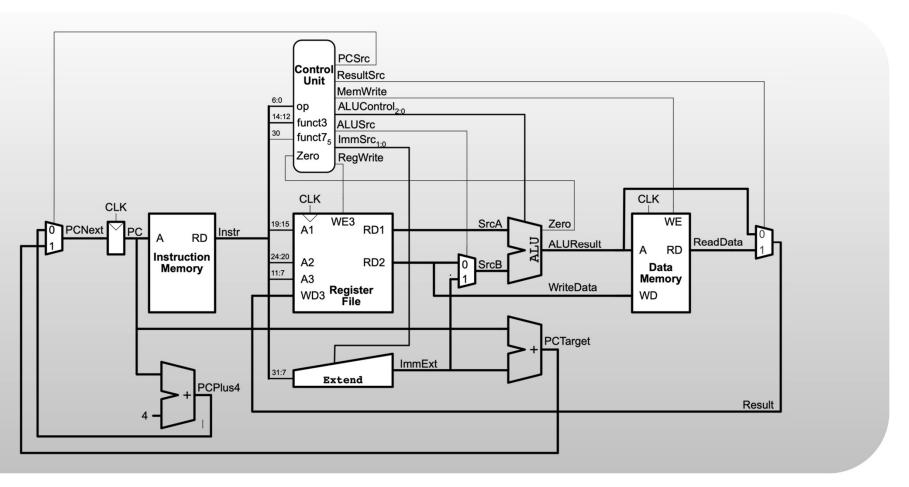

## Simple (Single-Cycle) RISC-V Computer

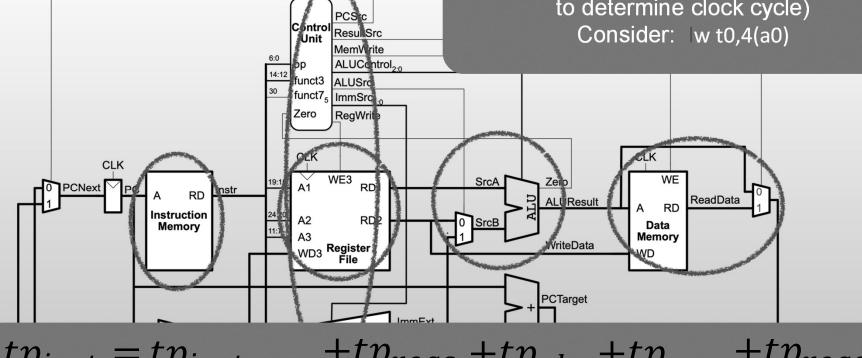

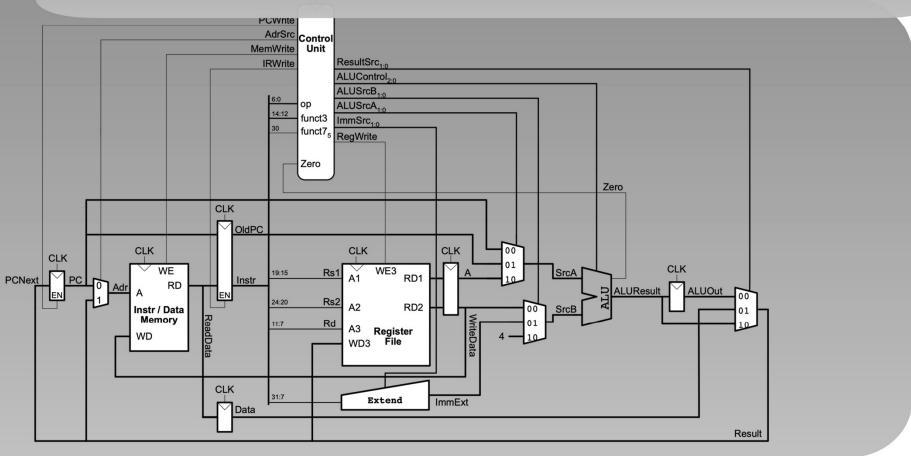

Identify items that are part of the "propagation delay" of an instruction. (Estimate upper bound that needs to be used to determine clock cycle) Consider: w t0,4(a0)

$$tp_{inst} = tp_{instmem} + tp_{regs} + tp_{alu} + tp_{ram} + tp_{regs}$$

# Consider Performance (prop delay) of Parts

Consider: add Consider: or Consider: sw Consider: lw

## Simple, Single-Cycle

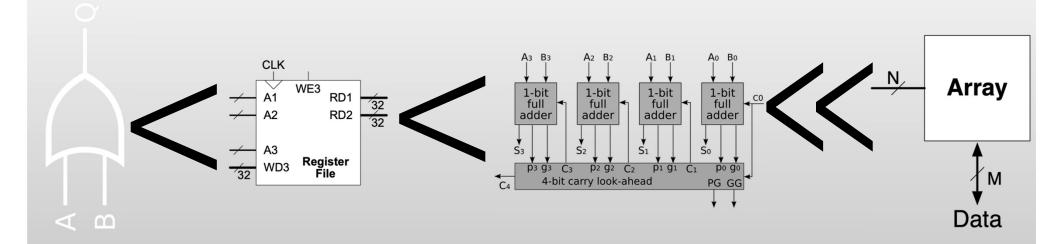

Consider times when adders are "working"

MOO I OOMPALOI

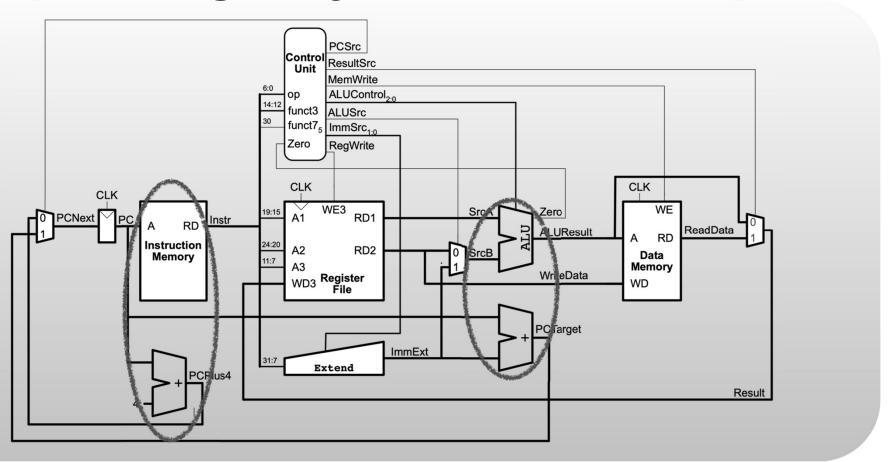

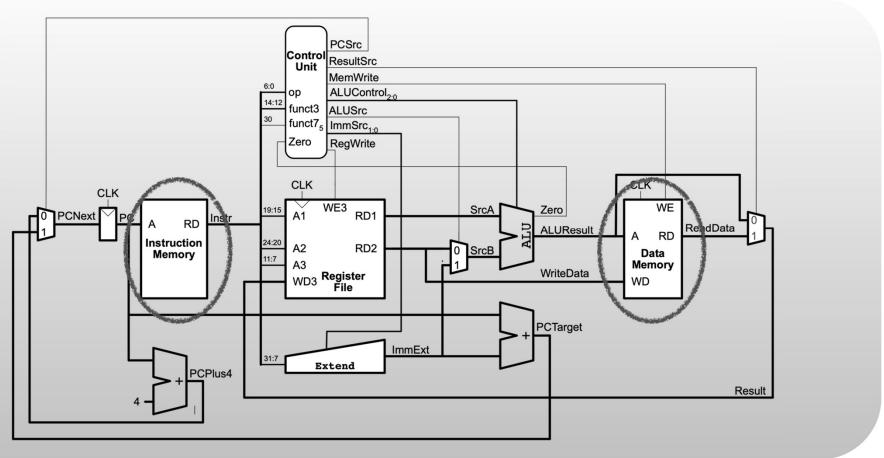

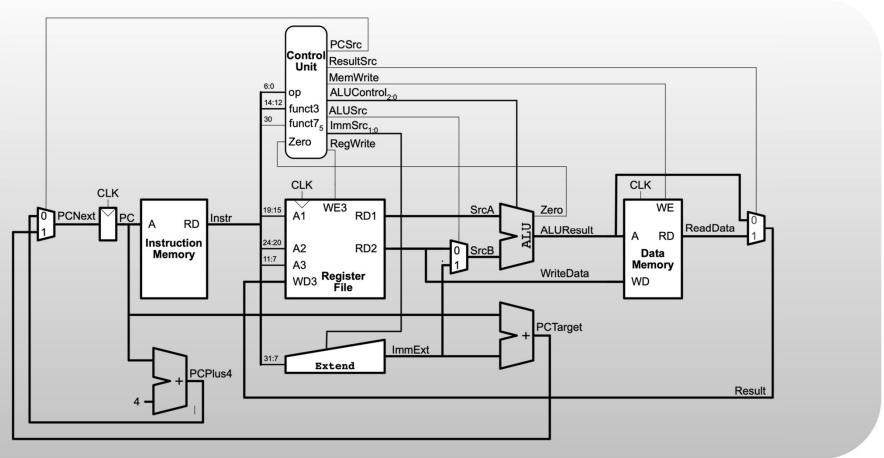

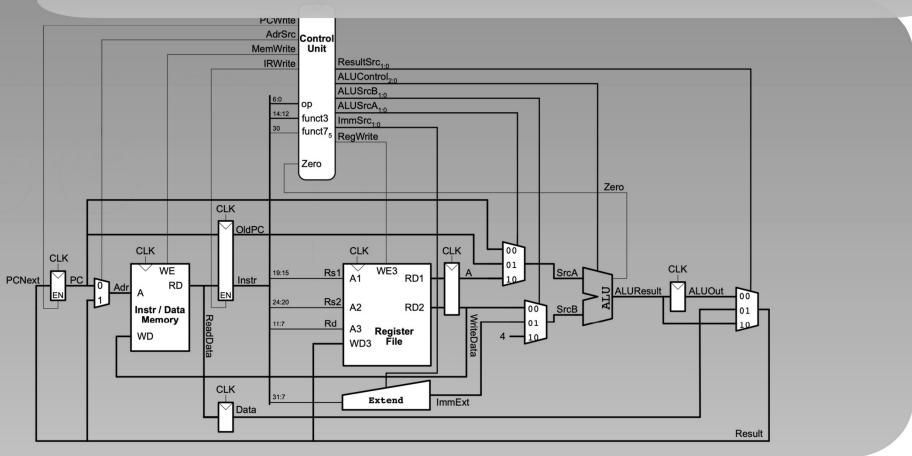

PICC-V Computer Simple, Single-Cycle Consider a sequence of instructions: add t1,t2,t3 PCSrc lw t4, 0(sp) Control ResultSrc MemWrite ALUControl<sub>3.0</sub> op funct3 ALUSrc funct7<sub>5</sub> ImmSrc<sub>1:0</sub> Zero RegWrite CLK CLK **CLK** WE3 WE SrcA Zero RD1 Instr RD ReadData **ALUResult** Instruction Memory Parts are "Idle" (done with their role in the instruction) most of the time. This is inefficient! Result

## Simple, Single-Cycle RISC-V Computer

#### **Architectures**

- Harvard Architecture

- Fixed program?

- Not so uncommon: Car, appliances, small electronics

- Questions: Are single-cycle things used? Yes.

- von Neumann

- General purpose: Magic of being able to change programs easily

- Programs (operating sys) can change program: "Computer", tablets, phones, ...

## Simple, Single-Cycle RISC-V Computer

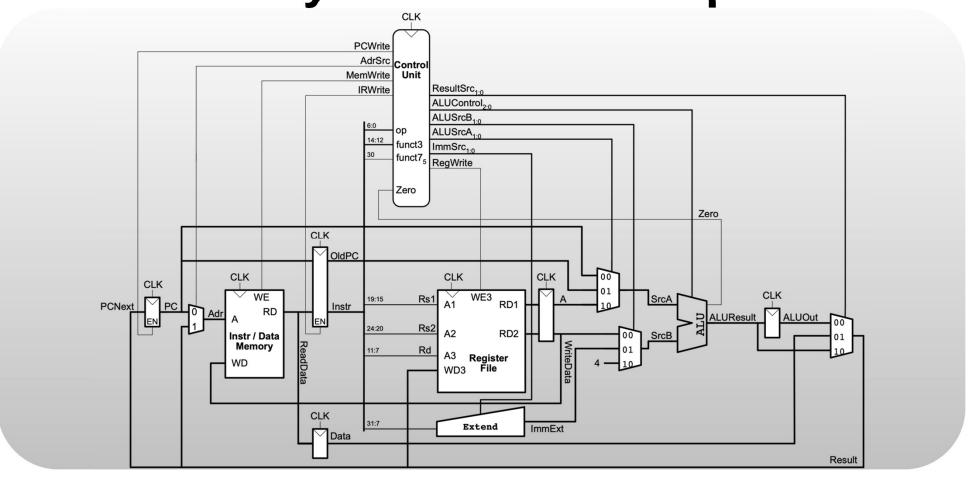

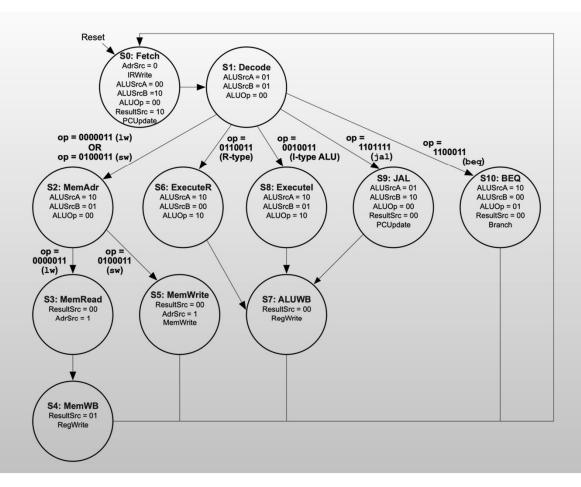

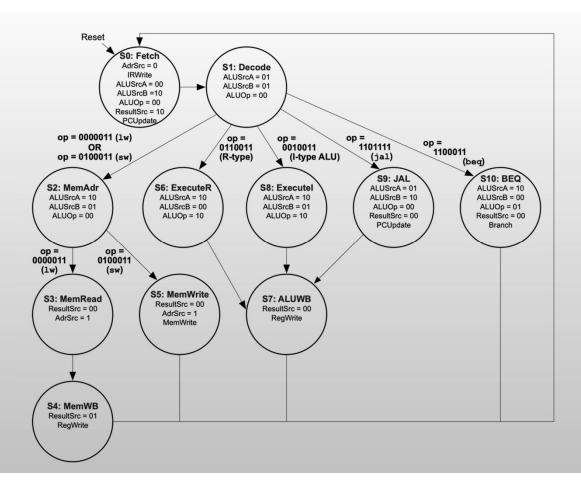

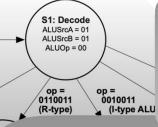

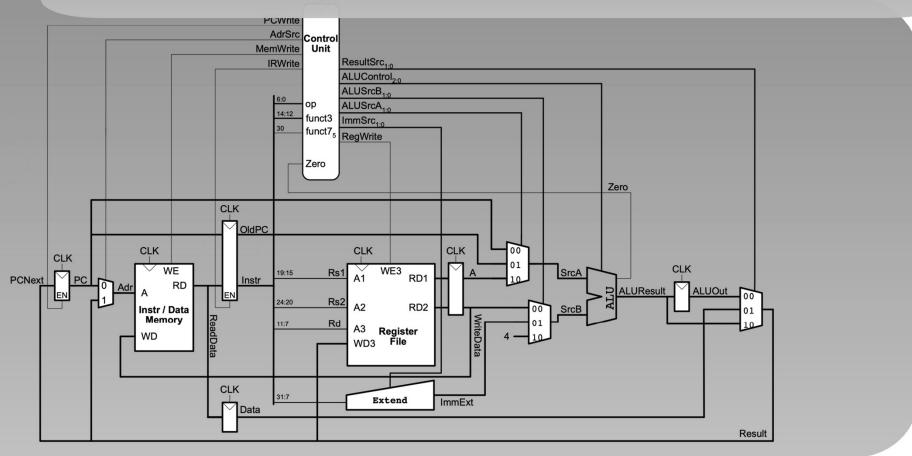

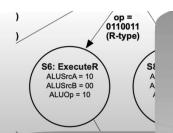

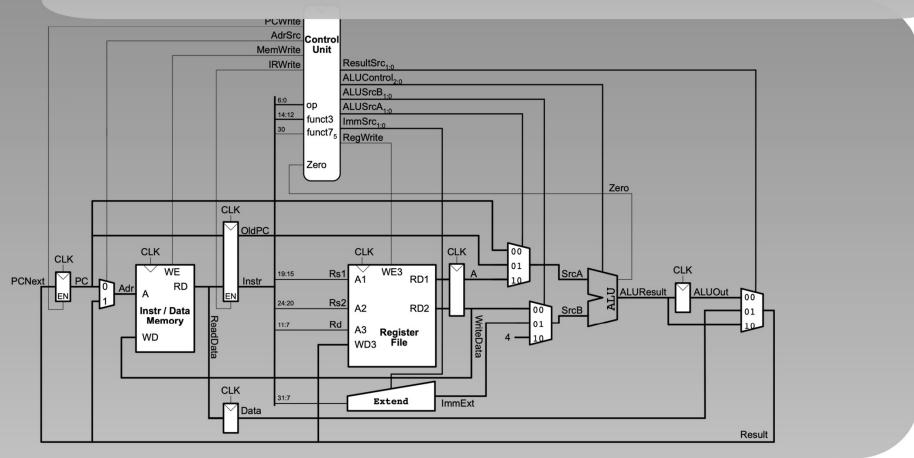

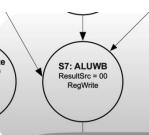

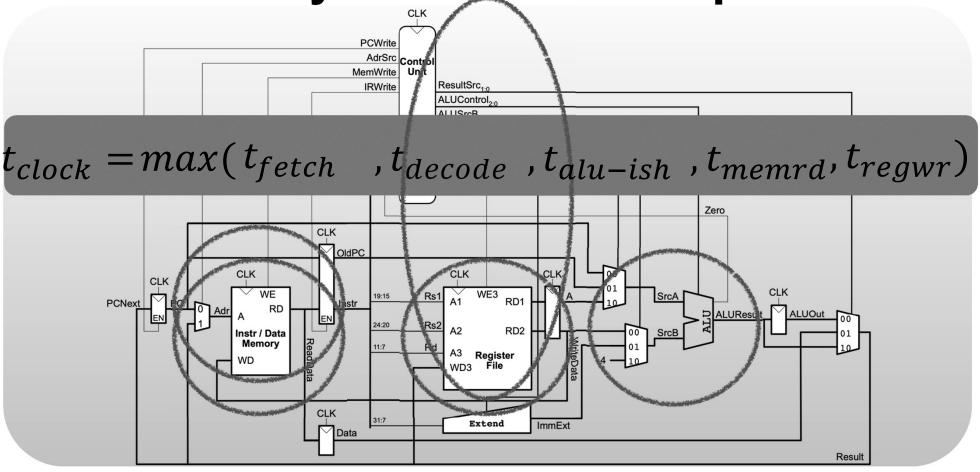

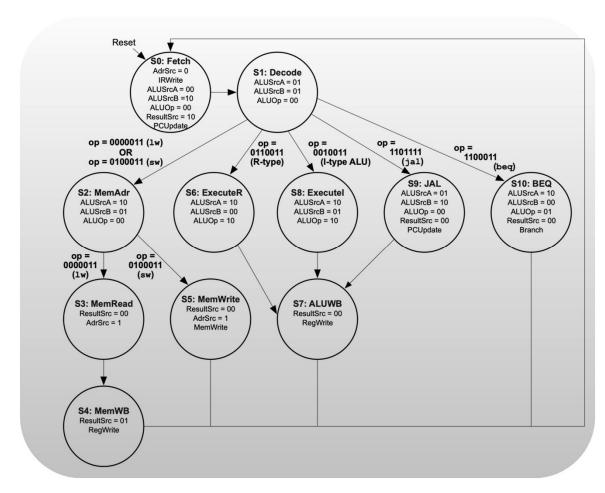

## Multi-Cycle RISC-V Computer

#### **Process**

### **Pros/Cons of Multi-Cycle**

- Instructions take only required time: Not constrained by the slowest instruction!

- A little more complex

# Questions: What do you think homework...

...hope we don't have to make the confusing state machine...

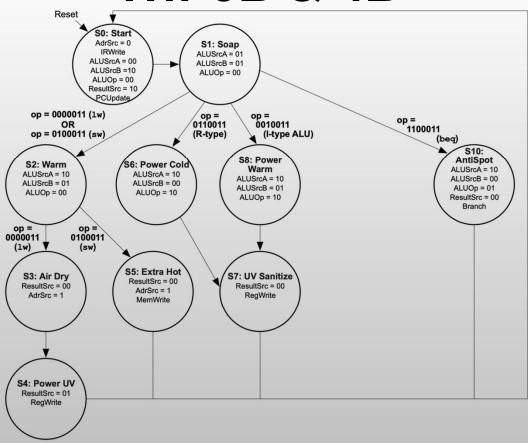

#### Good news!

#### **Process**

Already have - it's a Washer. Hw 3B & 4B

Multi-Cycle RISC-V Computer

#### **Instruction Times**

- 3-5 clock cycles

- Some instructions may be faster

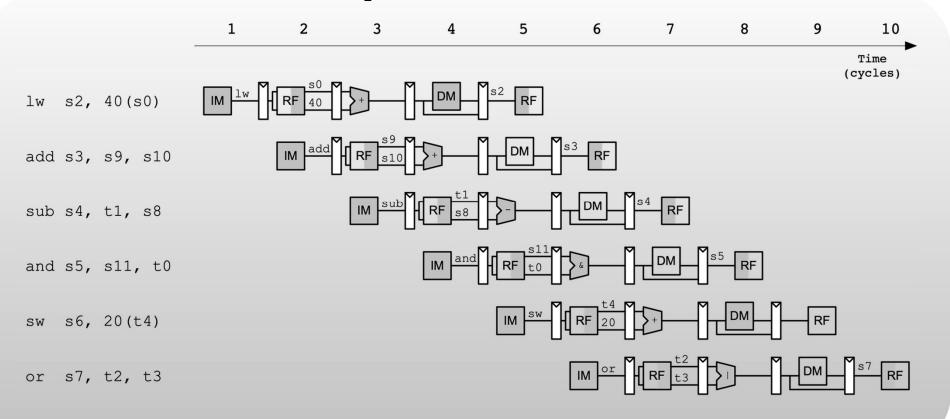

## **Next Improvement: Pipelines**

#### Laundry

- Laundry machines

- · Washer takes 30 minutes

- Dryer takes 1 hour (ugh)

- How long does it take to do 1 load of laundry all the way through?

- · What about 2 loads?

- What's the approx. average for 50 loads of laundry?

- What if I'm doing 12 loads of laundry and put something in on load 4 that I really need?

## A Pipeline / Factory

- My career: Develop Medical Equipment

- Along with....

#### **Customer Order**

- Body style / size

- "Flair" (style and color)

- Body shape

#### **Process**

- 1. Parts prep: read order, put order in bin, put part for order in bin

- 2. Slide bin down line to "assembler".

- 3. Slide down to cleaner

- 4. Slide down to packer

- 5. Move to shipping

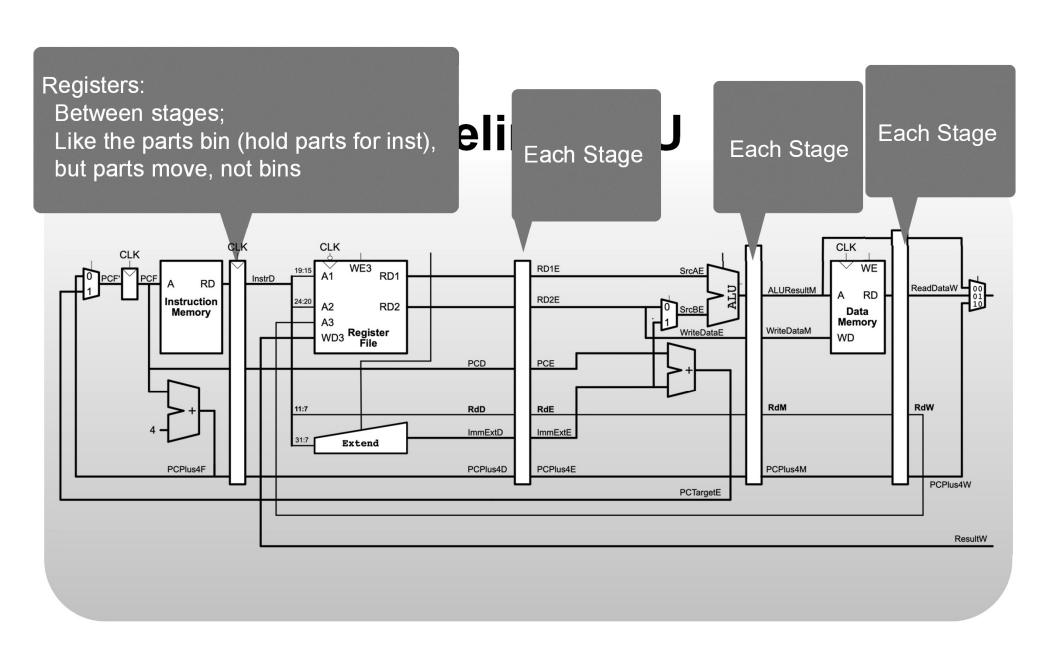

#### **Pipeline CPU**

#### **Instruction Time**

- Clock = Still controlled by slowest part

- Average instructions per clock = 1 cycle though!

- Significant improvement over prior...

#### Questions

- Why don't commercial microprocessors use 100 pipeline stages if increasing stages allows for higher frequency?

- In the HDL version of the pipeline, how are the stages and pipeline registers usually organized?

- When designing hardware in HDL, are there cases where the code compiles with no error messages but the circuit still doesn't work as expected? If so, what systematic methods do engineers use to debug and fix these kinds of "silent" bugs?

- How different do real CPU diagrams look from the RISC-V ones we have been studying in class?

- Which method of accounting for hazards is typically used in real pipelined processors, or is it problem dependent?

#### **Next Time**

• Studio!